文章图片

文章图片

晶体管微缩在 3nm 达到临界点 , 纳米片 FET 可能会取代 finFET 以满足性能、功率、面积和成本 (PPAC) 目标 。 对于 2nm 的铜互连 , 正在评估一项重大的架构变化 , 这一举措将重新配置向晶体管供电的方式 。

这种方法依赖于所谓的埋入式电源轨 (BPR) 和背面配电 , 让正面互连来传输信号 。 英特尔宣布将在其 20? 代(相当于 2nm)使用其 PowerVia 结构 , 其他芯片制造商正在评估类似方案 。

芯片制造商也可能会在 2nm 节点后尽快用钌或钼替代一定程度的铜 。 其他更温和的变化将使用低电阻通孔工艺、替代衬垫和完全对齐的通孔方法来扩展铜镶嵌互连 。

大部分优化发生在链中的薄弱环节——接触(金属 0)、金属 1 和通孔 , 其中 RC 延迟最有可能减慢

互连挑战始于光刻技术 , 在整个 5nm 工艺中都采用了 EUV , 这大大增加了成本 。

EUV 和 BEOL 图案化

在 7nm 节点 只有少数掩模层需要EUV光刻 , 但在 5nm(约 30nm 金属间距)时 , 这会变为 15 到 18 层 。 在光刻中 , 由于不精确对齐的特征 , 边缘放置错误 (EPE) 越来越受到关注 。 ASML研究员Robert Socha强调需要在 5nm 节点控制和减少 EPE 的贡献者 。 一个关键因素是覆盖误差 , 5nm 节点的覆盖预算仅为 2.5nm(5 个硅原子宽) 。

KLA过程控制解决方案总监 Andrew Cross 表示:“我们已经看到 EPE 预算中的叠加元素随着场内变化的增加而缩减得最快 。” “这导致更高的光学覆盖采样、改进的覆盖测量技术 , 以及在抗蚀剂显影和蚀刻后使用基于 SEM 的覆盖测量 , 这需要光学和电子束工具之间的协同作用 。 ”

通孔优化

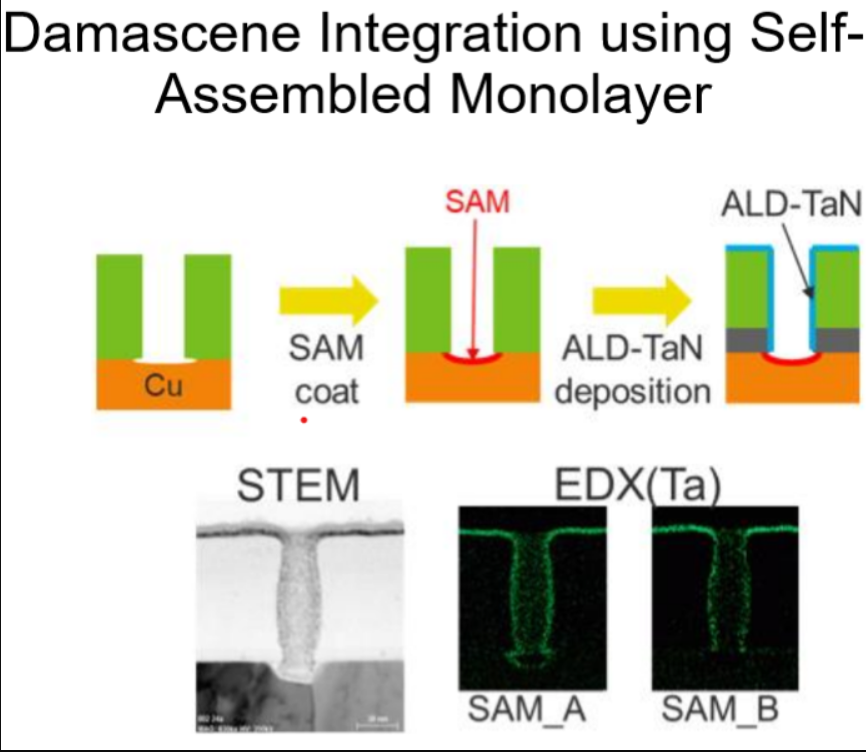

扩展铜技术的一个关键策略是消除铜通孔底部的阻挡金属 TaN 。 实现这一点的一种方法是通过选择性地沉积自组装单层 (SAM) 薄膜 , 通过原子层沉积来沉积 TaN(ALD) 沿侧壁 , 最后去除 SAM 并填充铜 。 在 IITC , TEL 使用双镶嵌集成描述了这样一个过程 , 并比较了两个自组装单层(A 和 B) 。 在 TaN 阻挡层 ALD 之后 , SAM 被蒸发 , 然后在通孔中进行铜化学沉积 (ELD)(见图 1) 。 在通孔预填充之后 , 通过 CVD 在沟槽侧壁上沉积钌衬垫 , 然后进行铜离子化 PVD 填充 。 使用 SAM B , 结果显示通孔底部没有 Ta (EDX) 。 任何 SAM

芯片制造商越来越多地将 SAM 工艺

另一种减少通孔底部阻挡金属 (TaN)

完全对齐的通孔 , 选择性沉积

完全对齐的通孔 (FAV) 背后的理念是减少通孔和线路之间的边缘放置错误的影响 , 这会导致器件故障和长期可靠性问题 。 自 32nm 节点以来 , 芯片制造商一直在采用自

- 芯片|直接不藏了!真我GT Neo3搭载独显芯片 插帧补偿游戏体验起飞

- 高通|三星35%低良率吓跑客户 消息称高通3nm订单转向台积电

- 芯片|?网友:有不少的外国高科技企业都将在中国的工厂给关了!

- 机器学习|ESP32芯片模组方案,运行机器学习算法,提升设备的数据处理能力

- 联发科|天玑8100+独显芯片!realme GT Neo3正面首度公布:超窄边框中孔屏

- iPad|首次升级自研M1芯片!iPad Air 5开售:4399元起

- realme|首款配备双芯片的天玑8100来袭!徐起:realme GT Neo3可以笑傲江湖了

- 1199元起,小米Redmi Note 11E开售:搭载天玑700芯片

- 智能手机|荣耀赵明:Magic 4要全面对标苹果 暂没有自研芯片的计划

- 芯片|别动不动就骁龙835再世