文章图片

本章旨在介绍和开发电信电信微波部门的LTCC作为一种新技术 , 以便设计和制造高性能和紧凑的微波和毫米波模块 , 这是传统包装技术不可能的 。 首先 , 我们简要解释了我们选择LTCC材料的动机 , 并将其与其他可用的商用磁带系统进行比较 。 接下来 , 我们将介绍LTCC的制造步骤 , 然后使用我们实验室的可用设备对该工艺进行验证 。 制造步骤包括胶带制备、通过和腔形成 , 通过填充、丝网印刷、堆叠、层压和共烧 。 然后 , 我们描述、调查和提出了在验证过程中遇到的技术问题的解决方案 。 最后 , 根据现有设备和已实现的测试瓷砖 , 定义了LTCC的设计规则 。

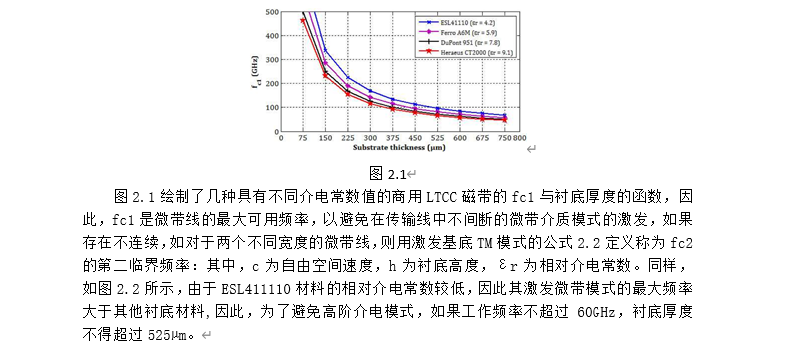

射频组件的设计过程从选择基材和金属化系统方面的最佳配合物开始 , 在微波和毫米波频率下封装时 , 选择合适的材料至关重要 , 因为它会影响系统的尺寸、阻抗和损耗 , 本节中将讨论的基板选择的另一个重要标准是最大工作频率限制 , 此外 , 在选择新的基材时 , 必须考虑的一个关键因素是所设计的传动线的几何参数 , 这对制造过程非常重要 。 微带介电模式或衬底模式可以在一个由支持高频TM模式的地面平面支撑的介电板上被激发 , 当介电衬底中的TM模与微带线的准TM模耦合时 , 问题就开始了 。

【esl|华林科纳关于LTCC技术中微波集成电路的封装报告】

为了避免丝网印刷过程中的困难 , 一个重要的考虑因素是选择一种相对介电常数较低的基底材料 , 这需要较宽的印刷线 。 根据基板厚度 , 针对一些商业LTCC磁带的先进设计系统(ADS?) , ESL41110磁带允许相对于其他LTCC磁带的最大的微带线 , 在一个燃烧的LTCC层(h=75μm)上的微条宽度约为140μm , 这可以简单地通过丝网印刷工艺来实现 。

LTCC电路的设计与某些混合和厚膜电路一样具有挑战性 , 根据层数(高达50层)和应用领域 , 增加了复杂性 , 一般来说 , LTCC电路的设计过程将从一个明确定义的概念或概念开始 , 然后 , 借助计算机辅助设计(CAD)软件、电路原理图、电磁(EM)建模和布局处理 , 对解决方案进行优化 , 以获得准确的设计和制造过程 。

在制造过程中 , 必须减少尺寸 , 以便能够使用更高的工作频率到毫米波范围 , 光刻工艺在LTCC上的应用使丝网印刷的尺寸和公差(在顶层)最小化 , 并允许我们的线宽和空间低至20μm(相对于丝网印刷中的100?120μm) , 我们的制造过程可以通过使用等静压而不是单轴压来改进 , 以更好地控制LTCC电路点火后的收缩 , 这也会减少层压过程中的空腔变形 , ESL41110材料的低介电常数允许在该磁带没有高阶模式激发的情况下使用毫米波段 , 但在77GHz(0.018)时其耗散系数相当高 。 对其他高介电常数LTCC材料的使用也可以进行探索 。

使用ESL41110LTCC材料进行了理论研究 , 使用ADS?和HFSS?软件对不同的射频结构进行模拟 , 测量通过内部开发的测试装置 , 在某些情况下使用直接安装在LTCC电路顶部的SMP连接器 , 测量结果与反模拟结果相近 , ESL41110提取的介电常数在1~30GHz之间在4.2~4.8之间 。 为了实现测量 , 实验室开发的用于LTCC电路测量的测试装置可以通过使用运行高达67GHz的末端发射连接器(来自西南微波)进行改进 。 此外 , 光刻工艺的发展将使在ESL41110衬底上使用具有细线和空间尺寸的CPW结构 , 从而允许在探测站中对LTCC电路进行表征 。

- 网络技术有限公司|阿里、美团入股华芯盛景创投中心

- 新能源|华为开源,“风鸿”集控系统发布,击碎新能源技术壁垒

- 华为荣耀|被华为“卖掉”之后,荣耀不负众望,Magic V首批评价已经出炉

- 5g|华为5G快报:西班牙刚做出错误决定,非洲就传来了好消息!

- 软件|华为的企业文化理念怎么就这么先进

- 中科大|华为任正非:“中国养的鸡,要回到中国的窝里下蛋!

- 华为|任正非:搞研发烧掉的1000亿,啥时候还我?徐直军:已经2000亿了

- 营收|营收下降近3成,但仍拿500亿分员工,华为发出大红包

- 华为|任正非感慨真正对华为“卡脖子”的,并非美国而是中国人!

- 企业家|任正非:让贫穷的老百姓来救华为,我良心上过不去,那马云呢?