文章图片

文章图片

文章图片

文章图片

文章图片

【it芯片|【FPGA学习】如何创建使用IP核-PPL?】

文章图片

文章图片

文章图片

文章图片

文章图片

什么是PPL?PLL是一种反馈控制电路 , 其特点是利用外部输入的参考信号控制环路内部震荡信号的频率和相位 。

Quartus II软件提供了锁相环PLL的IP核 , 对时钟网络进行系统级的时钟管理和偏移控制 , 具有时钟倍频、分频、相位偏移和可编程占空比的功能 。

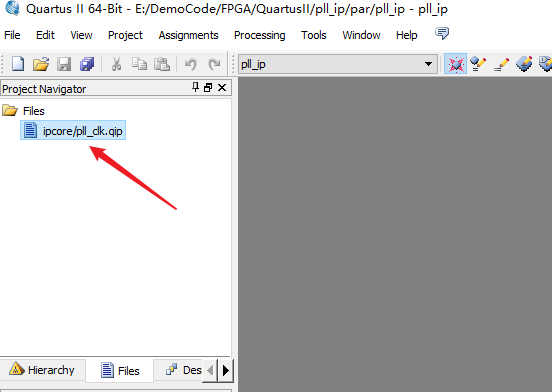

创建PPL的IP核1、创建新建工程参照新建例程

2、工具栏添加IP核

“菜单栏 - Tools - MegaWizard Plug-In Manage”3、配置IP核运行环境

选择目的 , 由于新创IP核 , 故选择“Create”

选择PLL核

配置PLL核运行环境 , 即可点击“Next”芯片为“Cyclone IV E”系列编程语言为Verilog HDL

- 参数设置

速度等级一般设置为8;

输入时钟频率 , 为50MHz

PLL类型 , 在“Cyclone IV E”系列中只有一个选择

正常模式:

在标准模式下 , PLL对GCLK网络所产生的延迟进行完全补偿 。 正常模式中的内部时钟是与输入时钟管脚相位对齐的 。 在此模式中 , 外部时钟输出管脚会产生相对于时钟输入管脚的相位延迟 。 因此 , 这种模式一般用于产生FPGA内部用时钟 , 不将时钟输出给FPGA外部使用 。

源同步模式:

如果数据和时钟同时到达输入管脚 , 那么在I/O单元输入寄存器的数据与时钟端口 , 数据与时钟之间的相位关系保持不变 。 此模式可用于源同步数据传输 , 只要I/O单元上的数据与时钟都使用同一I/O标准 , 这两个信号就会经历类似的缓冲器延迟 。

零延迟缓冲模式:

在该模式下 , 外部时钟输出管脚与时钟输入管脚是相位对齐的 , 没有延迟 。 当使用该模式时 , 需要在输入时钟与输出时钟上使用同一I/O标准 , 以确保输入与输出管脚上的时钟对齐 。 因此 , 这种模式一般用于FPGA给外部输出时钟信号 。

无补偿模式:在该模式下 , PLL不对任何时钟网络进行补偿 。 这种模式能提供更佳的抖动性能 , 因为反馈到PFD中的时钟不经过某些电路 。 相对PLL输入 , PLL内部以及外部时钟输出均有相位偏移 。 因此 , 一般不选用这种模式 。

- 性能真的是旗舰唯一?我并不认为,从荣耀全新旗舰定位聊起

- 王传福|比亚迪高端芯片问世,外国车企高价购买,王传福坚决不卖

- 智能物流|极兔将在沙特建立智能物流产业园

- 芯片|老美也扛不住的“背后”,外媒指出关键点!这一切或将是假象?

- 第一财季|因芯片短缺持续存在,英飞凌预计 2022 年收入目标约 147 亿美元

- 程序员|注册资本仅190万,却获得华为青睐,这家芯片公司是何方神圣?

- 苹果|芯片和系统都是美国控制的,所以苹果能完全脱离中国供应链

- 芯片|全球芯片业销额十年内或翻番,冲刺6.4万亿规模!美国快扛不住了

- 5G|冬奥信赖联通力量|联通5G 大国实力

- 金立|金立新机上线,苹果外观+虎贲芯片,售价529起可还行?