文章图片

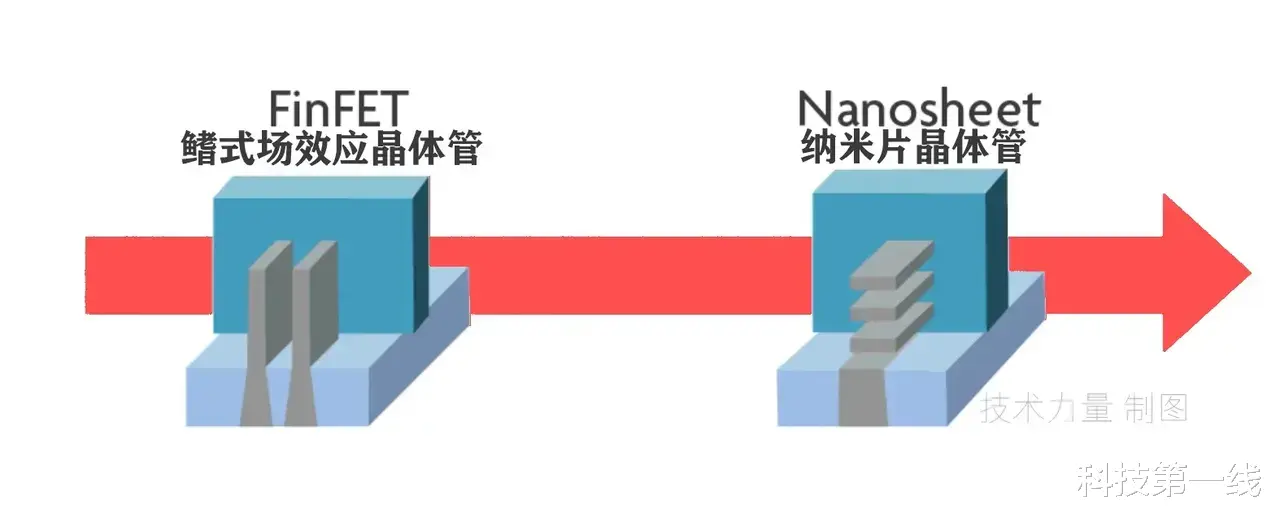

近日 , 台积电公布未来芯片制造路线图:2纳米芯片已确定采用纳米片晶体管工艺 。 未来几年 , 台积电将采用如下技术路线图:从现有的鳍式场效应(FinFET)晶体管到纳米片(Nanosheet)晶体管 , 然后采用叉片式(Forksheet)晶体管 , 最终进步到垂直互补(CFET)晶体管 。

现有的FinFET只能做到3纳米芯片 , 因为鳍片宽度来到5纳米时 , 这种技术已经达到其物理极限 。 从2025年开始 , 台积电将开始生产2纳米制程芯片 。 纳米片晶体管工艺是由IBM研究院开发的 , 它采用更宽的纳米片去驱动晶体管的电流以及改进静电特性 。

纳米片工艺的具体实现流程有4步:

1 , 使用外延生长的多层Si硅和SiGe硅锗来定义器件通道 , 在衬底上形成超晶格结构 , 一个堆栈至少由三层硅锗和三层硅组成 。

2 , 使用极紫外光刻机为纳米片架构蚀刻凹陷内部隔离层 , 这种隔离层是一种额外的电介质 , 用于将栅极与源极/漏极隔离以降低电容 。

3 , 分离纳米片 , 释放纳米片通道 。

4 , 集成RMG替代金属栅极 , 包括在纳米片层周围和之间的功函数金属的沉积和图案化 。

【芯片|有点意外!台积电公布未来芯片制造路线图!】台积电将在今年底开始生产3纳米芯片 , 这预示FinFET工艺技术即将走向终结 。 台积电预计3纳米向2纳米芯片的过渡大约需要3年时间 。

- 芯片|大规模扩产:86条晶圆产线,才建了35条,芯片就要不缺了,这可咋整?

- 消息传来,美对台积电、ASML摊牌了

- 芯片危机即将结束?汽车行业要告别至暗时刻了

- 一加科技|盘点4款旗舰手机:618给我们带来意外惊喜,等等就能省1000多元

- |Reno8 Pro+极限视频挑战:拍摄难题迎刃而解,这块芯片立大功

- 苹果|比强更强!苹果M2芯片终于来了:性能暴涨,功耗反而降低了

- 芯片|世界先进称显示驱动芯片订单恐超预期下滑

- 芯片|努力但是没能力的员工到底要不要淘汰?马云给出了自己的答案

- 芯片|比缺少芯片更严重,制造业被外资垄断,毫无挣扎之力!

- 芯片|苹果发布iOS16等操作系统,以及搭载M2芯片的两款笔记本电脑