文章图片

文章图片

文章图片

文章图片

火龙888镇楼

众所周知 , 骁龙888系列是个笑话 。 搭载骁龙888的安卓手机 , 发热大 , 耗电快 , 性能峰值上不去 , 结合在一起用一个词概括:废物 。 当然这不是高通第一次如此头铁了 。 上一次这么热 , 是7年前的骁龙810 , 因为过热造成体验降级 , 直接把索尼LG等一堆高价日韩系手机干没了市场份额 。 而上上次这么热 , 是13年前 , 超频到800MHZ的高通MSM7225系列 , 直接让还能继续战斗1年的windowsMobile6.5系统手机全线提前市场消失 。 所以说 , 高通是有原罪的(确信) 。

那问题来了 , 为何骁龙888采用的三星5nm工艺 , 包括骁龙810采用的台积电20nm工艺 , MSM7225系列采用的第一代台积电65nm工艺 , 都这么热?芯片制程不是越小越好嘛?

摩尔规律

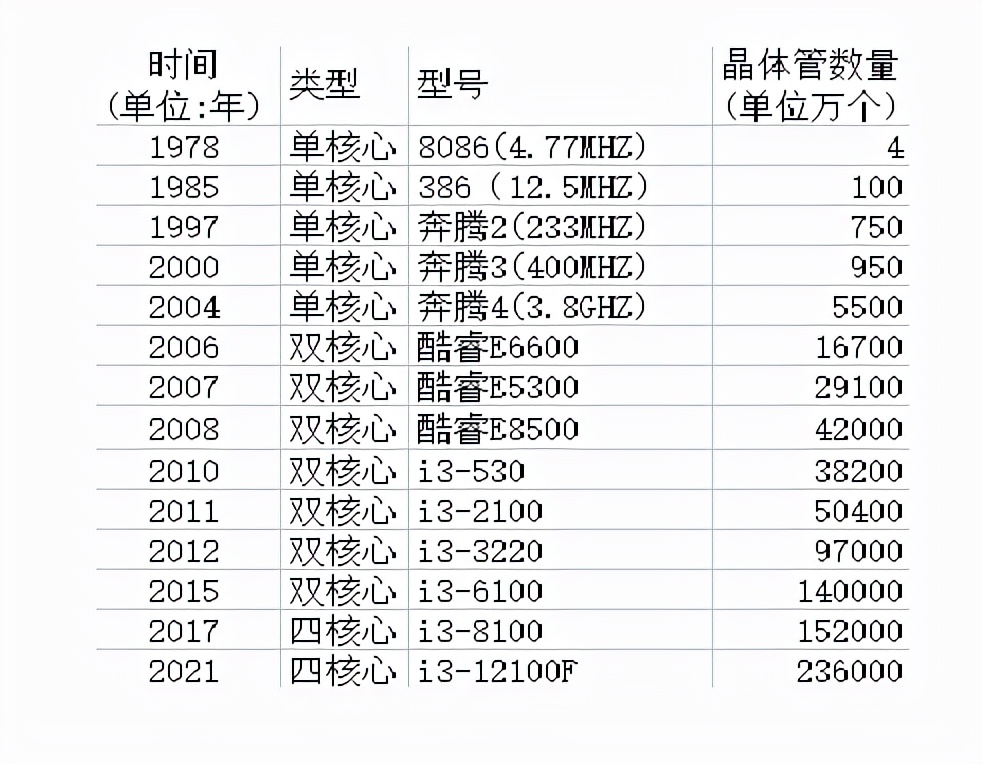

大家都知道一个摩尔定律 , 其实就是戈登摩尔总结的半导体发展规律 , 版本很多 , 但是显然英特尔那边的说法是 , 每24个月 , 半导体晶体管规模跟性能要翻一倍 。 结合本系列前几篇的说法 , 确实如此嘛 , 从1960年代开始 , 芯片晶体管跟频率都在不断增加 。 半导体工艺也越缩越小 , 确实如此 。

60年来晶体管翻了6万倍

晶体管结构在物理层面足够大的时候 , 不断缩小是可行的 。 但是如果晶体管达到一个非常小的规模的话 , 比如达到一个很小的程度 , 小到不能阻止电子漏出通道的程度 , 那这个工艺本身就会发热漏电耗电严重了 。 而这个节点 , 并不是眼前的什么1nm之类“先进工艺” , 而是20世纪初的65nm工艺 。 从1996到2005年10年时间 , 65nm工艺困扰了人类很久 , 始终无法低成本量产65nm芯片 , 无论IBM , 英特尔还是AMD 。 而当时的大量芯片 , 都卡在90nm工艺接近10年 , 比如ARM789全线处理器 , 游戏机 , 甚至包括英特尔自己的PXA移动处理器系列 。 有个常识就是 , 65nm并不比90nm工艺更省电 , 甚至静态功耗还要多 , 这就是高通MSM72XX系如此拉垮的原因 。 这样可以快进到芯片制造现在面对的更大的一个问题 , 量子隧穿效应下2nm能不能实现都是疑问 。

某百科的原话:隧穿电子是指发生隧穿的电子(废话) 。 隧穿效应是一种量子特性 , 是电子等微观粒子能够穿过它们本来无法通过的“墙壁”的现象 。 这就说的很明白了 , 当“墙壁”的“缝隙”足够电子乱窜 , 特别是“墙壁”的“砖头”足够小的时候 , 那墙壁就失去了作用嘛 。 65nm时代就有低配版的这个问题出现 , 解决时间是10年 。

量子隧穿

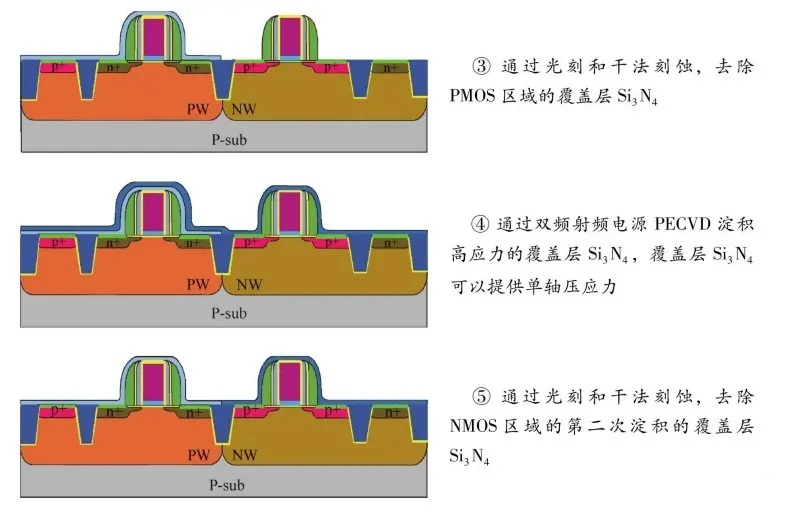

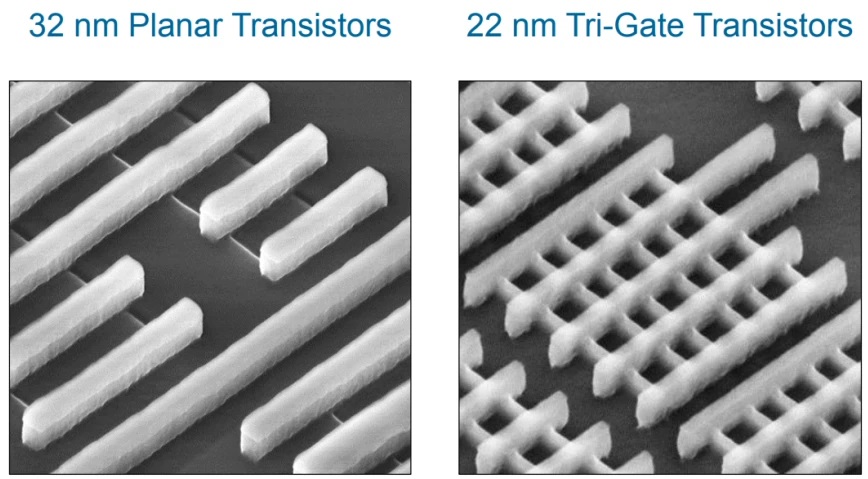

以2000年前后来说 , 传统芯片制造模式 , 是以IBM技术指导路线加整个日本工艺技术生产经验定义的 。 整个芯片内部电路排布 , 从头到尾都是平面铺开设计的 。 这也是传统意义上的电路布局嘛 。 特别是尼康佳能的光刻设备阵列 , 也是这个思路一路延伸 。 但是如果芯片缩小到了一个程度 , 电子泄漏 , 电路通电会收到互联线的磁场干扰 , 这会让频率上不去 。 这就是串扰(crosstalk) , 以及噪声(noise) , 这也是当时英特尔宣布不玩频率战争的一个理由 。

- 今天,这些小米手机全面降价!

- 官方直降400元,12GB+512GB+E5旗舰屏,还买什么小米12?

- 苹果开发者大会将于6月7日线上举办,B站回应强行开启HEVC播放,比亚迪否认涨价,柔宇科技否认全员放假,这就是今天的其他大新闻!

- 小米科技|小米MIX FOLD 2曝光 或采用360°折叠屏 6月份发布

- 小米科技|小米开启米粉节,最高降4000元,这4款降幅大

- 设计师|华为开始反击,鸿蒙新品终于出现,可以和苹果说声再见了

- 折叠屏|折叠屏手机销量预测:三星、荣耀、小米成赢家,共计近1800万部!

- vivo x|vivo X80 Pro跑分曝光?蔡司影像大突破,黑科技满满,值得期待!

- 小米科技|小米12X:虽少人问津,但冲进了三月好评榜第二名!

- 显卡|鲁大师2022年3月手机流畅榜:小米MIUI系统确实已王者归来