文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

在很早以前 , PCIe便成为了服务器总线的主流解决方案 。

随着大数据、人工智能、云计算等领域的发展 , 服务器内的高速硬件数据交互需求变得愈发紧迫 , 迫使PCIe标准在近些年实现了跨越式发展 , 在PCIe 5.0还未走进我们生活时PCIe 7.0都已在制定之中 。 今天 , 就让我们聊一聊PCIe那些事儿 。

PCIe总线是什么

在PC领域 , CPU想与包括硬盘在内的硬件“交流” , 需要借助一条名为“I/O总线”的通道 。

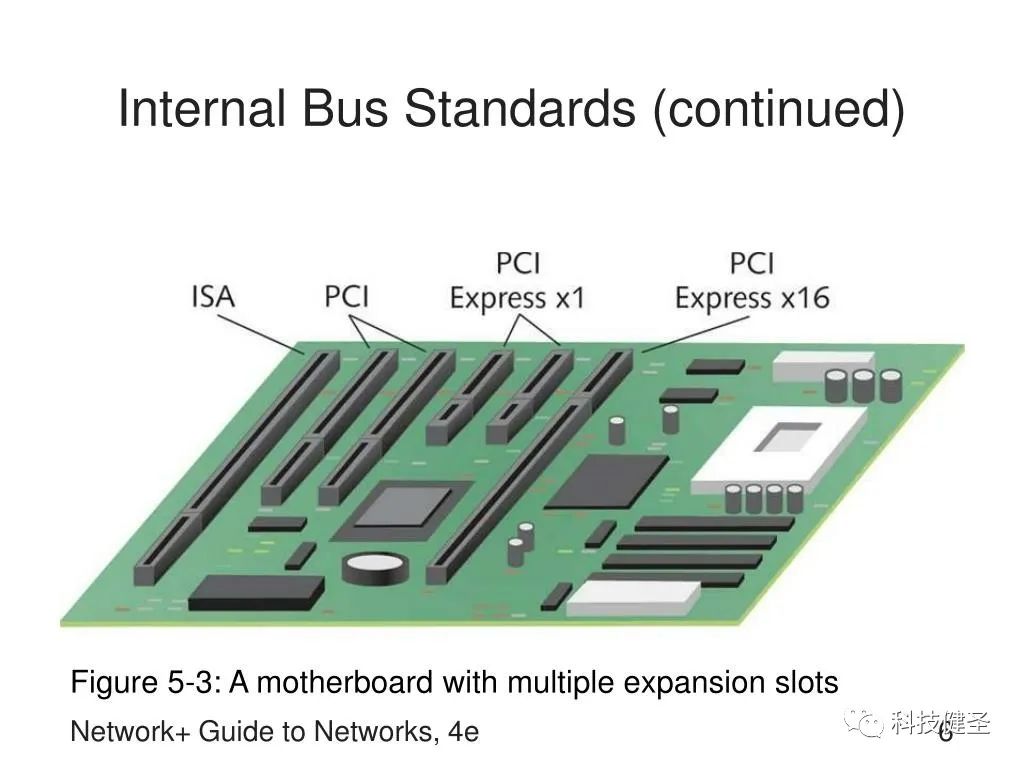

历史上 , 第一代I/O总线通常是指ISA、EISA、VESA和Micro Platforms;第二代I/O总线则包含PCI、PCI-X和AGP 。

2001年 , 英特尔在IDF大会上首次提出了第三代I/O总线3GIO的概念(直到2003年才正式商业化) , 后经PCI-SIG(PCI特殊兴趣组织)认证发布后才改名为PCI-Express(Peripheral Component Interconnect Expres) , 拥有PCIe和PCI-E两种缩写名称 。

简单来说 , PCI-Express(下文简称PCIe)是一种高速串行计算机扩展总线标准 , 具备高速串行、点对点双通道、高带宽传输、抗干扰能力强、传输距离远、功耗低、(新标准)向下兼容(老标准 , 需匹配的驱动配合)等优点 , 自诞生之后便参与到连接显卡、固态硬盘以及采集卡和无线网卡等外设的任务中 。

通过PCIe连接的外设能获得多少速度 , 取决于该PCIe链路由多少条通道(Lane)构成 。

【CPU|512GB/s带宽直破天际!一文读懂面向未来的PCIe 7.0总线!】在消费级市场 , PCIe链路可以支持1、2、4、8、12、16个通道 , 即×1、×2、×4、×8、×12、×16的PCIe链路 。

初代PCIe 1.0能在一条通道 (×1) 上实现单向2.5GT/s(约250MB/s , 详细计算方法请见下文)的总吞吐量 , 在×16通道下的双向总理论吞吐量为8GB/s 。

到了最新的PCIe 7.0 , 其在×1通道上单向吞吐量就高达128GT/s(16GB/s) , 在×16通道下的双向总理论吞吐量将达到惊人的512GB/s , 较之初代提升了整整64倍 , 如果和更早的133MB/s总线相比更是增长了480倍!

吞吐量的计算方式

按照PCI-SIG组织的最初设想 , PCIe标准每更新一次 , 传输速率就会翻倍一次 。

不过 , 由于编码方式和有效数量出现了变化 , 所以历代PCIe标准在计算每一条Lane支持的吞吐量时会出现细微的变化 。

比如 , PCIe 1.0和2.0编码的有效数据是8b/10b方案 , 即每传输8个bit , 需要发送10个bit 。 以PCIe 1.0为例 , 2.5GT/s的传输速率意味着每一条通道上支持每秒钟内传输2.5G个bit , 因此其每一条Lane支持的吞吐量就是2.5GT/s × 8 ÷ 10 =2000Gbps , 再用2000Gbps ÷ 8就能将bit转换为Byte , 也就是说PCIe 1.0×1的单向吞吐量为250MB/s , 双向为500MB/s 。

- CPU|经常急着出门?这四款手机的快充几乎达到极致,参数也都很均衡

- 第二代骁龙8果然有隐藏大招!CPU、GPU一起打鸡血

- CPU|为什么说 CPU 是人造物的巅峰?

- 高通|第二代骁龙8果然有隐藏大招!CPU、GPU一起打鸡血

- CPU|好评率最高的四款手机,几乎“0差评”,轻松用至2025

- CPU|好评率最高的四款手机,几乎“0差评”,轻松用至2027

- AMD|AMD明年初推出非X型号CPU 规格售价提前看下

- 华为荣耀|荣耀X50再次堆料,骁龙870坐镇,16+512GB超大储存加持!

- CPU|营收下滑,利润却上升!腾讯,下了很大的“功夫”

- |为什么推荐购买256GB手机而不是512GB?