英特尔|未来十年架构创新的“灯塔”,英特尔揭开XPU的第二篇章( 三 )

文章插图

据悉,目前英特尔已与大多数超大规模云服务提供商建立了紧密的合作关系。同时,英特尔还公布首个ASIC IPU:Mount Evans(研发代号),这就是英特尔与一家一流云服务提供商共同设计和开发的,它融合了多代FPGA SmartNIC的经验。GPU Ponte Vecchio,堪比登月难度的创新近年来,在百亿亿次计算愿景和人工智能等新兴数据中心应用的驱动下,GPU与CPU的协作已经成为现代数据中心重要的创新方向。作为XPU战略中与此密切相关的核心产品,Ponte Vecchio的亮相备受关注。

文章插图

英特尔Ponte Vecchio首席架构师Masooma说,“Ponte Vecchio是我在30年的芯片开发生涯中开发的最复杂的芯片,在合作伙伴以及IP、测试、封装、制程技术和制造团队的帮助下,我们有幸把这个架构变成现实。”

文章插图

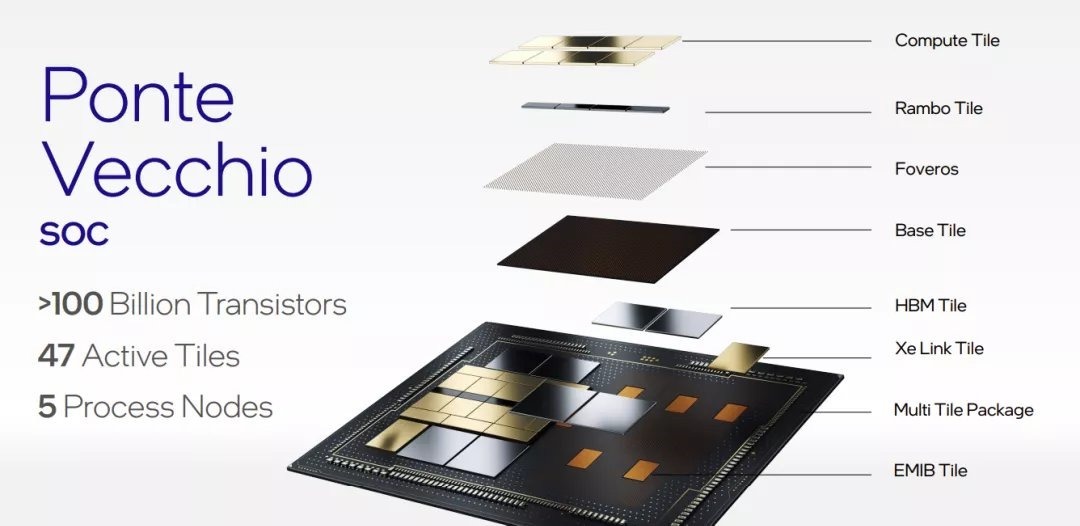

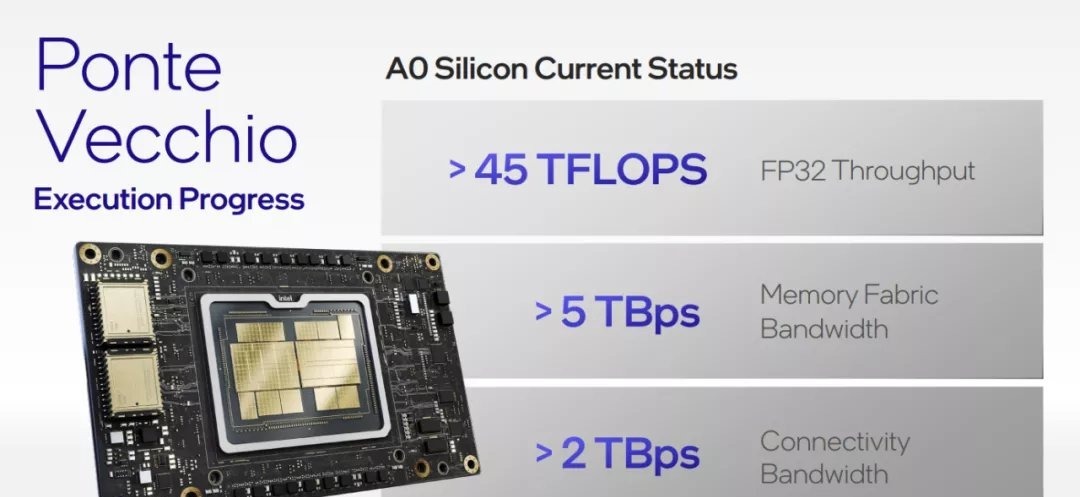

作为 “堪比登月难度创新的一款产品”,Ponte Vecchio背后又有哪些故事?据了解,面向百亿亿次计算的 GPU——Ponte Vecchio,是英特尔至今最复杂的 SoC。它基于 Xe HPC 微架构,并采用多种先进的半导体制程工艺、英特尔的 EMIB 技术以及 Foveros 3D 封装技术,包含 1000 亿个晶体管,可提供业界领先的浮点运算性能和计算密度。早期的 Ponte Vecchio 芯片就展示了出色的性能,在流行的 AI 基准测试中创造了推理和训练吞吐量的行业记录。比如 A0 版芯片输出了高于 45 TFLOPS 的 FP32 吞吐量,超过5 TBps 的内存结构带宽,以及高于 2 TBps 的连接带宽。

文章插图

在这次架构日上,英特尔分享了一段演示视频,其中两个与Ponte Vecchio相关的数据——ResNet 推理性能超过 43000 张图像/秒和超过每秒 3400 张图像/秒的 ResNet 训练性能让人印象深刻,这两项性能都有望实现行业领先。据悉,Ponte Vecchio 已走下生产线进行上电验证,并已开始向客户提供限量样品,预计将于 2022 年面向 HPC 和 AI 市场发布,而且已被在建的百亿亿级超算系统Aurora选中,用作其核心算力组件。做架构创新的“灯塔”面向数据中心架构,除了IPU和GPU,英特尔还透露了下一代至强可扩展处理器Sapphire Rapids的更多细节。

文章插图

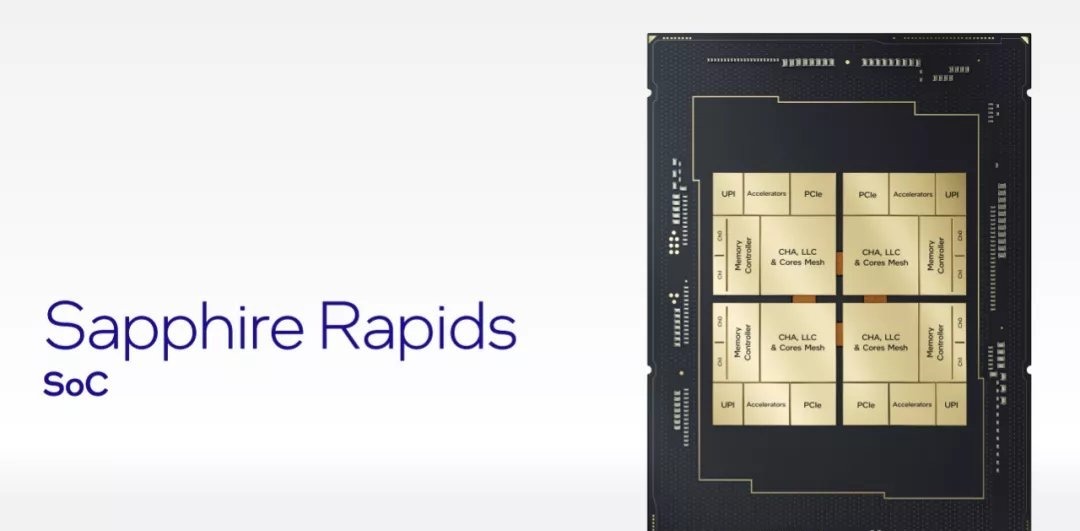

英特尔首席数据中心架构师Sailesh说,“Sapphire Rapids是我们下一代至强可扩展处理器。它能够提供卓越的开箱即用的性能,为数据中心内广泛的工作负载和部署模式带来增强功能。”

文章插图

Sapphire Rapids的诞生背景,还是为了实现弹性计算模型(如容器化微服务)的突破性能,以及在所有形式的、以数据为中心的计算中快速扩展 AI 的应用。具体来说,Sapphire Rapids的核心是一个分区块、模块化的SoC架构,采用英特尔的嵌入式多芯片互连桥接(EMIB)封装技术,在保持单晶片CPU接口优势的同时,具有更优的可扩展性。Sapphire Rapids提供了一个单一、平衡的统一内存访问架构,每个线程都可完全访问缓存、内存和I/O等所有单元上的全部资源,并基于此在整个SoC上实现一致的低时延和高横向带宽。很明显,这样的设计除了可实现了巨大的性能提升之外,还可让这些性能核拥有与之匹配的缓存,并发挥即将到来的DDR5和PCIe5.0的威力,更好地平衡计算、内存和I/O。所以2022年,我们很可能会见到结合了英特尔的性能核与全新加速器引擎的Sapphire Rapids,并亲眼见证它变身为下一代数据中心处理器的标准。站在今天这个原点,这些丰富的架构创新,既代表了过去十年英特尔的技术积累,也映射出未来十年英特尔要引领的行业趋势和创新方向。一句话总结的话,那就是从过去到现在,从CPU到XPU,英特尔始终是架构创新的“灯塔”。

- 打脸!华为在美国,用专利把英特尔、苹果、微软、高通打败了

- 本周华为小米相继报出的新闻,让我看到中国科技公司未来发展希望

- 云曦灵|对象终于能包分配了?百度希望未来两年实现“数字人自由”

- 沉浸式|海外观察丨未来 10 大科技趋势预测全解读(上)

- 三星|这一招漂亮!英特尔对华“宣战”48小时内,中方果断亮出一张王牌

- 芯片|又一巨头或对英特尔“下手”,美方希望重掌芯片制造,机会渺茫!

- javascript|帕特·基辛格被任命为英特尔CEO已有一年

- 英特尔|Intel未发布下代至强被开盖:完整64个核心、只开启56个

- 交易|直击二手电商市场:流量红利逐渐消失后,二手电商的未来在哪?

- 英特尔|朝7家企业“下手”,英特尔启动新计划!原来中芯只是一个开始?