半导体|半导体制造关键工艺装备CMP:全球双寡头格局,国产装备崛起( 二 )

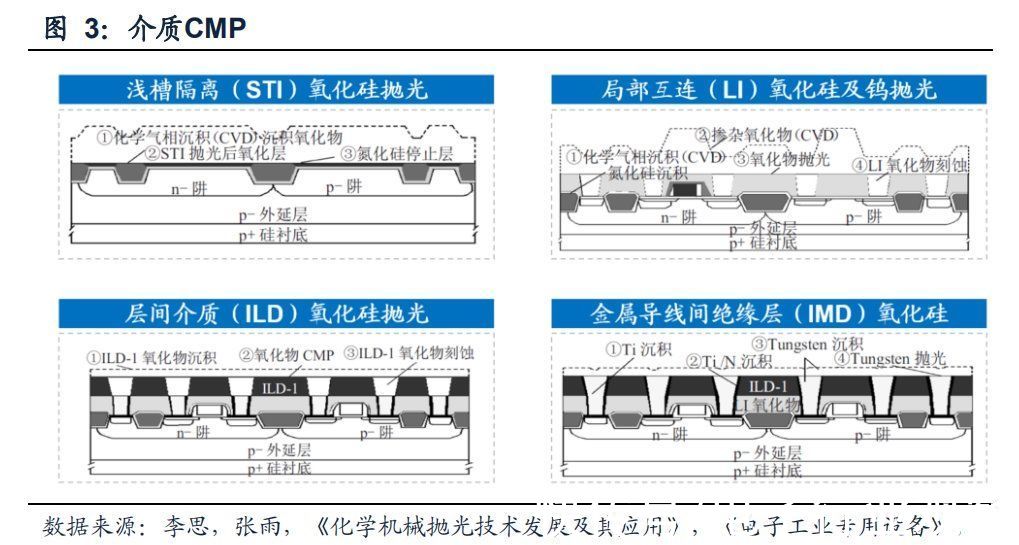

ILD-CMP/IMD-CMP:ILD-CMP指的是层间介质(ILD)抛光,IMD-CMP指的是金属内介电层(IMD)抛光,主要抛光对象是二氧化硅介质。作为芯片组件隔离介质,集成电路制造工艺中最常被使用的介电层是相容性最佳的二氧化硅介质。二氧化硅膜的CMP大多应用在层间绝缘膜及组件间的隔离(Isolation)平坦化工艺中。

ILD-CMP(层间绝缘膜平坦化)将导线或组件上的层间绝缘膜平坦化,以便完成接下来的多层互连线工艺,是完成多层互连结构的基础,为大规模集成电路工艺中不可缺少的步骤。IMD-CMP(元器件间隔离膜平坦化)目的在于形成平坦的氧化硅膜(组件与组件间的绝缘隔离层)。在层间绝缘膜的平坦化方面CMP对象还有等离子体增强化学气相沉积(PECvD)膜、硼磷硅玻璃膜(BPSG)及热氧化膜(Thermalox记e)等。

文章插图

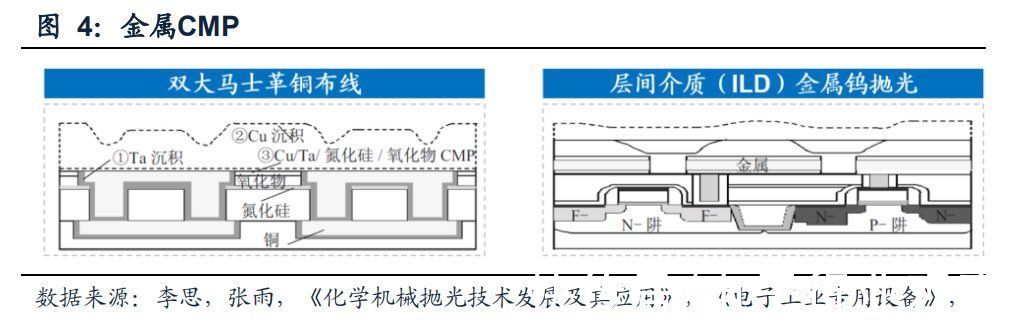

Cu-CMP:随着集成电路层数的不断增加,在铜布线工艺中新的层间导线连接方式“接触窗”得到广泛应用,这种工艺方法也称为“大马士革工艺”(Damascene)。大马士革工艺,首先在两层电路间的绝缘膜上进行刻蚀,使之形成凹槽(接触窗),再进行连接金属导线膜的沉积,最后以CMP方式去除金属膜。在双大马士革中,Cu-CMP用来抛光通孔和双大马士革结构中细铜线,双大马士革工艺过程中用介质作为停止层。

文章插图

(二)抛光技术与清洗、工艺控制技术并重

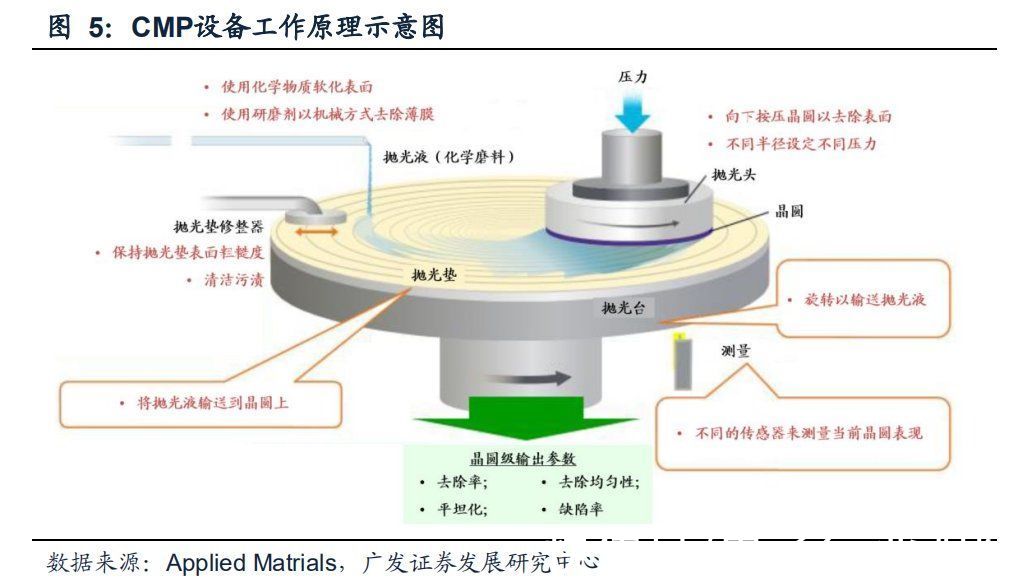

【 半导体|半导体制造关键工艺装备CMP:全球双寡头格局,国产装备崛起】CMP的作业原理:抛光头将晶圆待抛光面压抵在粗糙的抛光垫上,借助抛光液腐蚀、微粒摩擦、抛光垫摩擦等耦合实现全局平坦化。抛光盘带动抛光垫旋转,通过先进的终点检测系统对不同材质和厚度的磨蹭实现3~10nm分辨率的实时厚度测量防止过抛,更为关键的技术在于可全局分区施压的抛光头,其在限定的空间内对晶圆全局的多个环状区域实现超精密可控单向加压,从而可以响应抛光盘测量的膜厚数据调节压力控制晶圆抛光形貌,使晶圆抛光后表面达到超高平整度(例如全局平整度要求是10nm,则相当于面积约440000平方米的天安门广场上任意量带你的高低差不超过0.03毫米),且表面粗糙度小于0.5nm,相当于头发丝的十万分之一;此外制程线宽不断缩减和抛光液配方愈加复杂均导致抛光后更难以清洗,且对CMP清洗后的颗粒物刷领要求呈指数级降低,因此需要CMP设备中清洗单元具备强大的清洁能力来实现更彻底的清洁效果,同时还不会破坏晶圆表面极限化微缩的特征结构。

文章插图

对CMP设备而言,其产业化关键指标包括工艺一致性、生产效率、可靠性等,CMP设备的主要检测参数包括研磨速率、研磨均匀性和缺陷量。

(1)研磨速率:单位时间内晶圆表面材料被研磨的总量。

(2)研磨均匀性:分为片内均匀性和片间均匀性。片内均匀性指某个晶圆研磨速率的标准方差和研磨速率的比值;片间均匀性用于表示不同圆片在同一条件下研磨速率的一致性。

(3)缺陷量。对于CMP而言,主要的缺陷包括表面颗粒、表面刮伤、研磨剂残留,这些将直接影响产品的成品率。

为了实现这些性能,CMP设备需要应用到纳米级抛光、清洗、膜厚在线检测、智能化控制等多项关键先进技术。CMP产品的技术水平也主要取决于设备在抛光、清洗、工艺智能控制等核心模块/技术的表现。具体可以分为两大类:

(1)抛光技术。可以实现纳米尺度的“抛的光”、晶圆全局“抛得平”,这是CMP工艺的基础。

- 酷睿处理器|关键数据出炉,京东比阿里差远了

- CPU|元宇宙+高端制造+人工智能!公司已投高科技超100亿,股价仅3元

- 智能制造|企业转型的新时代,夹缝中求生存

- 央媒表态后,联想关键数据出炉,柳传志这回要扳回一局?

- 阿里巴巴|被苹果无辜“踢出局”,引发央视点名,国产制造该何去何从?

- 芯片|又一巨头或对英特尔“下手”,美方希望重掌芯片制造,机会渺茫!

- 中国半导体产业进入了技术驱动成长期 半导体及元件板块短线拉升|板块异动 | 拉升

- 大众网·海报新闻记者 单姗 单文玲 潍坊报道为助力企业健康快速成长|“小巨人”华特磁电“磁”实发展 跑出潍坊制造业加速度

- 产业链|航空装备制造行业产业链全景梳理及区域热力地图

- 芯片|全球仅有,能设计并制造出5nm芯片的,不是苹果更不是台积电