3D打印|芯片设计浅析(前端流程部分-下)

文章图片

文章图片

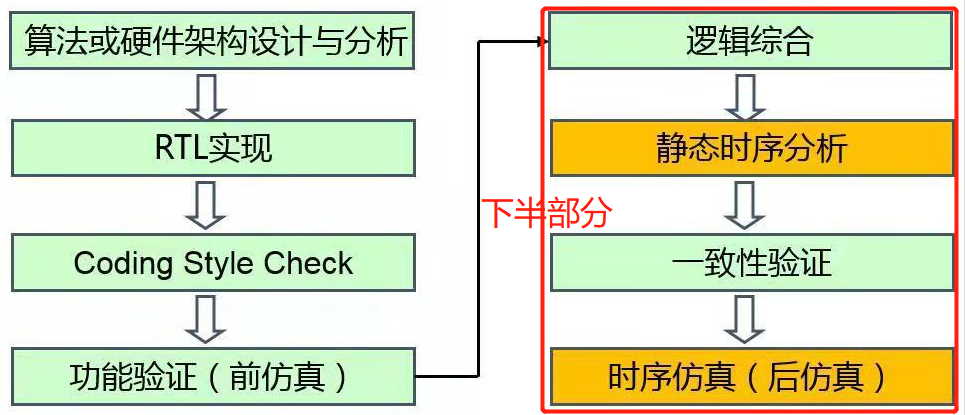

承接文章《芯片设计浅析(前端流程部分-上)》本篇为下半部分内容 。

(5)逻辑综合

逻辑综合是一个虚拟与现实的分界点 , 意思就是说前面4步都是虚拟的 , 编写代码等相关设计 , 而到逻辑综合过程 , 就需要考虑实际的芯片生产 , 包括工艺的物理特性 , 电特性等等因素 。

因为逻辑综合需要基于特定的综合库 , 不同库中的如门电路的时序参数 , 标准单元面积不同 , 因此综合出来的电路在时序 , 面积上是不一样的 。

它需要将VerilogHDL格式的文本转变为工艺库相关的网表格式文本 , 这个网表包含了RTL中所有的逻辑信息 , 当然还可能会有DFT(离散傅立叶变换) , clock goting(门控时钟) I/O等 。

输出文件中还包含有标准延迟文件SDF:它包含了网表中所有器件的延迟信息 , 用于时序仿真

(6)静态时序分析(STA)

全称为“Static Timing Analysis” , 是专门对于时序的分析 , 静态分析需要保证芯片设计中所有的路径 , 满足内部时序单元对建立时间和保持时间的设计要求 。 也就是说无论信号的起点是什么 , 信号都可以被及时地传递到该路径的终点 。

它主要是在时序上对电路进行验证分析 , 检查电路的setup time和hold time是否违例 。 如果出现时序违例时 , 是无法正确采样和输出数据的 。

(7)一致性验证

这个验证就是验证RTL代码和第5步的逻辑综合后的网表是否一致 , 那怎么去判断呢?简单来说 , 还是利用逻辑关系 , RTL代码和逻辑综合都可以抽象成由节点和边构成的图 , 然后比较两幅图是否一致 , 来验证整体设计是否正确 。

常用工具:Formality Conformal

(8)时序仿真

对芯片实际工作时的工作状态进行仿真 , 来验证功能是否正常 , 所以会同时包含动态时序仿真 , 静态时序仿真 。

总体来说 , 芯片的数字前端设计(也称规律设计)是逻辑设计 , 它以设计架构为起点 , 以实现目标功能和目标时序的网表为终点 , 用逻辑电路实现其预期的功能 。

至于想要得到一块完整的具有高性能能的芯片 , 前端完成之后就是芯片设计的后端部分了 , 后端部分也是对于前端设计的物理实现 。

【3D打印|芯片设计浅析(前端流程部分-下)】

- 华为|麒麟芯片+6000毫安电池,华为畅享50现身,水滴屏设计!

- 芯片市场关键消息传出,中科院做对了!

- nas|可否用国产28nm芯片生产全国产低档手机,占领低端市场?

- 本文转自:法治日报2022年6月5日|《火箭设计师的工作日志》

- 股价|阿里和腾讯加入,国产芯片在AI、云计算、物联网多点开花

- 基于SSM的植物花草养护交流网站平台设计与实现

- 操作系统|从备受争议到一片好评,OPPO Reno8设计戳中了哪些行业痛点?

- 芯片|ARM宣布罢免中国董事长,有何影响?或比芯片断供更可怕?

- 芯片|华为突然上架两款5G手机,麒麟芯片+鸿蒙OS,花粉:终于等到了

- |森海塞尔新旗舰无线耳机:新的设计,更多的功能,以及标志性声音