文章图片

文章图片

文章图片

如果说前几年是互联网工资高 , 涨薪 , 跳槽薪资翻倍的新闻层出不穷 , 那现在这个“对象”则从IT变为芯片设计 。

但是对于IT还比较好理解 , 就是编程 , 做网站 , 做APP , 智能算法等等 , 那芯片设计是个什么玩意呢?

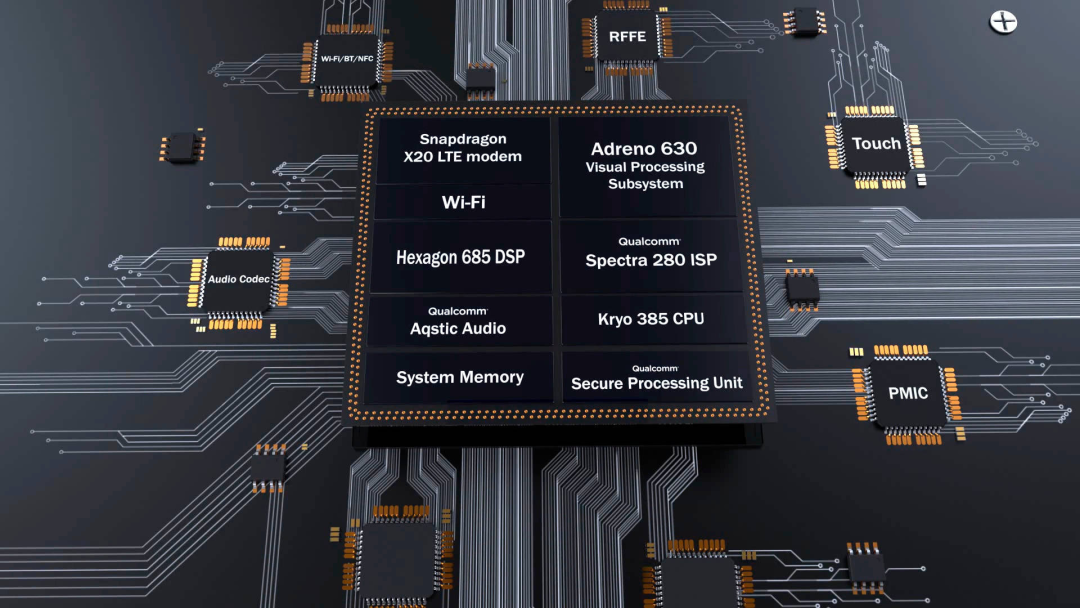

【芯片设计|芯片设计浅析(前端流程部分-上)】芯片设计和IT编程一样 , 也分“前端”和“后端” 。 不过和IT不同的是 , IT中的前端是用户所看到的那些酷炫的APP界面 , 网页界面 , 后端是逻辑关系 , 而芯片设计中的前后端则对比IT有点像反过来的 , 芯片设计前端是对逻辑关系的设计 , 后端是可以被“看到”的物理层的实现 , 包括一个个物理大小和位置的单元 , 连线等 。

本篇主要介绍芯片设计前端流程部分

(1)算法或硬件架构设计与分析

就像搭建房子一样 , 首先需要在大脑中有一个规划 , 专业的会有一份建造的图纸 , 所需的材料物料清单等等 , 芯片设计也是一样 , 在设计之初需要对芯片中的数字部分的高层次算法或架构进行分析和建模 , 这里的算法构建会用到编程语言(算法离不开编程) , 不同类型的芯片会有不同的偏好选择 。

这部分也是整个芯片设计的核心 , 奠定了之后整个芯片的性能和功耗 , 它需要为硬件提供一个正确的软件功能模型 , 然后通过大量的仿真和调试 , 为下一步的RTL实现提供总体性的设计验证指导 。 当然 , 具备这部分工作技能的人员也是社会上最缺的一类人才 。

常用的工具语言:MATLAB , C++ ,C , System C System Verilog等

(2)RTL实现

就是根据第一步的架构设计结果 , 转化为Verilog HDL进行实现 , 所以可以理解为第一步是统筹规划 , 第二步是具体去实现 , RTL实现的输出结果就是转化为了Verilog HDL输出 。

Note:

Verilog HDL是一种硬件描述语言 , 它以文本形式来描述数字系统硬件的结构和行为的硬件编程语言 , 可以用以表示逻辑电路图 , 表达式等逻辑输出 。

常用的工具:Vim Emac

(3)Coding Style Check(编码检查)

检查RTL实现步骤的代码 , 排除代码中的一些问题或错误 , 比如Clock Domain Cross(时域交叉) Lint等等 , 一般也需要实时考虑同步异步时钟信号的问题 , 比如芯片中的数字部分采用局部同步和全局异步 , 就需要在设计中注意跨时钟域的数据同步问题 。

常用的工具:Syglass LEDA

(4)功能验证

仿真 , 验证芯片设计过程中是否存在bug , 包括各项预定功能检查 , 工作状态检查等 。 为了芯片的稳定性 , 这个阶段的过程时间会比较长 , 数以月计 。

常用的工具:Modelsim VCS NC-Verilog

前面4个部分可以看成是虚拟的芯片工程设计过程 , 至于后面的实现在第5~8部分内容 , 是前期设计验证阶段之后的实现部分了 , 包括逻辑综合 , 静态时序分析 , 一致性验证以及时序仿真 。

由于篇幅内容长短问题 , 下半部分后面更新 。

- jenkins|AMD劲敌登场!英特尔13代酷睿芯片要来了:兼容现有主板

- 芯片|光子芯片领域实现突破,打破技术封锁,美方有人提议:炸掉台积电

- Redmi|爆款预定 Redmi 11首度曝光:搭载台积电7nm芯片天玑700

- 芯片|手机处理器天梯图,芯片CPU、GPU性能排行榜

- 抖音|大屏看书就是香!10英寸墨水屏设计的电纸书:墨案inkPad X简评

- Intel|平均年薪86万元 消息称Intel美国芯片工厂领先台积电

- 他26岁博士毕业即为特聘副教授,为中国芯片做出贡献

- 软件|传京东方失去3000万块iPhone14屏幕订单,因擅改设计

- 这家国产芯片的崛起,叫板美日韩芯片企业

- 高通骁龙|联发科芯片真的崛起了吗?天玑8100性能竟然超越了骁龙870