IBM|三星与 IBM 联手推进半导体芯片设计的突破

文章插图

【 IBM|三星与 IBM 联手推进半导体芯片设计的突破】今年在加利福尼亚州旧金山举行的第 67 届国际电子器件会议上,三星和 IBM 在他们关于“设备级 3D”的讨论中宣布,两家科技公司合作在设计技术上取得了重大突破。下一代半导体芯片。这项新技术允许晶体管垂直堆叠,从根本上提高了功率效率或更高水平的性能。

三星和 IBM 展示突破性 VTFET 半导体技术,提供更高水平的生产力和效率

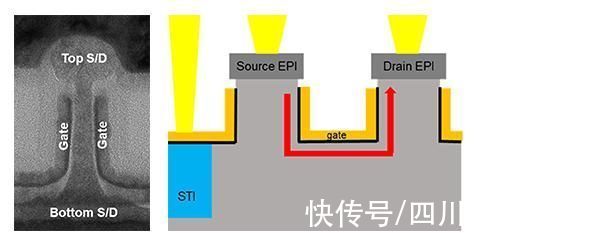

在谈话中,两家公司解释了如何通过将电流从水平方向重定向到垂直方向,不仅可以减小半导体芯片的尺寸,还可以使它们更加强大和高效。

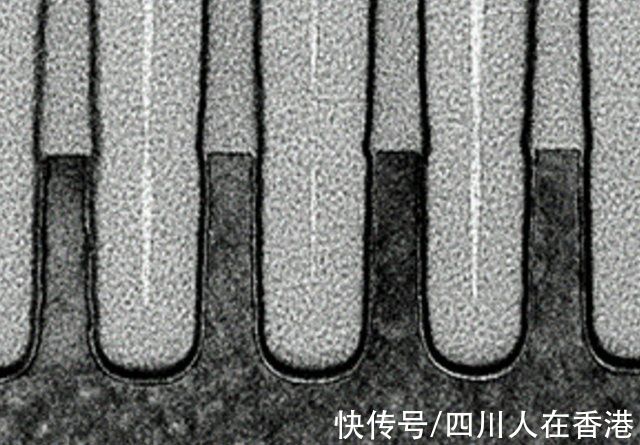

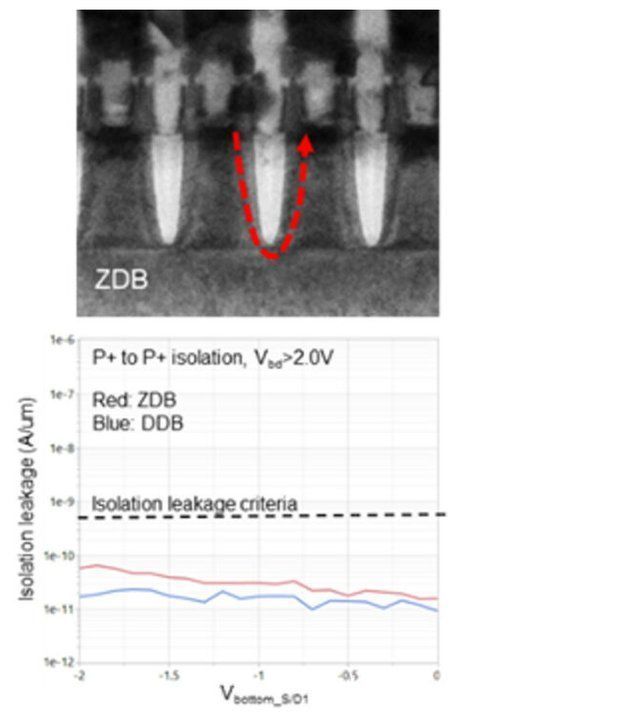

根据摩尔定律的预测,CMOS 晶体管以横向或横向方式构建,几十年来的无数进步缩小了它们的尺寸,因此现在可以将数十亿个晶体管放入芯片中。但是进一步缩小晶体管以提高芯片性能和增加新功能是困难和昂贵的。将它们垂直放置而不是水平放置会节省空间并更容易延长摩尔定律的寿命吗?受基于沟槽的 DRAM 垂直存取晶体管的启发,IBM 和三星的一个团队将描述他们如何改变晶体管架构,在体硅上使用所谓的垂直传输纳米片 (VTFET) 和 45 纳米栅极构建 CMOS 器件沥青。

-论文 #26.1,“用于横向传输器件之外的 CMOS 扩展的垂直传输纳米片技术”,H. Jagannathan 等人,IBM/Samsung

以前,半导体芯片将平放在硅表面上,而电流则水平流动。这种新设计允许晶体管垂直放置,而不是平行于半导体芯片的表面。新技术将使制造公司能够绕过摩尔定律的限制性能,从而因低功耗而节省能源。

文章插图

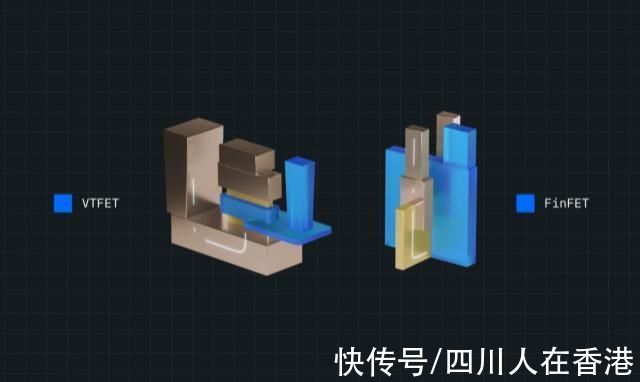

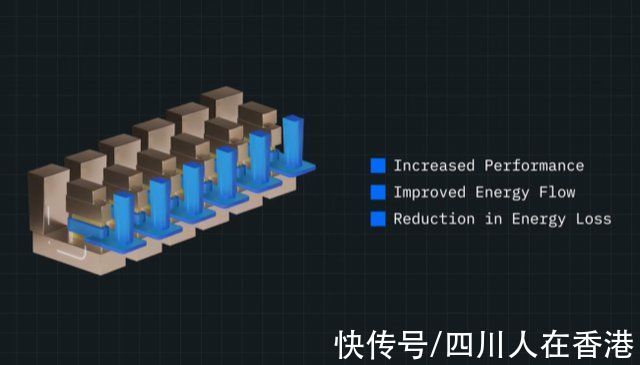

三星和 IBM 为提高效率和性能而垂直堆叠晶体管的努力被称为垂直传输场效应晶体管,或 VTFET。与当前的 FinFET 结构设计相比,两家公司之间的合作有望提供两倍的性能,或高达 85% 的功率效率提高。加密货币矿工将看到能源效率的提高,环境的影响也将从本质上得到改善。

文章插图

文章插图

文章插图

垂直器件提供了持续缩放的机会,因为栅极长度和间隔尺寸--决定栅极间距(晶体管之间的距离)的两个关键因素--可以以水平无法实现的方式进行优化。此外,由于降低了静电和寄生损耗(SS=69/68 mV/dec 和 DIBL= 为了验证这一概念,研究人员使用 VTFET 来制作功能性环形振荡器(测试电路),与横向设计参考相比,这表明电容减少了约 50%。

文章插图

目前还没有关于何时在商业产品级别上看到新的 VTFET 技术的消息。英特尔以及其他科技巨头都以创造新的埃级芯片而著称,英特尔估计发布日期为 2024 年最后一个季度的某个时间,以英特尔 20A为品牌。

#科技#

举报/反馈

- 副董事长|京东方A董秘回复:公司与全球数千家供应商保持着良好的合作关系

- 微信|个人收款码与商业收款码有什么不一样

- 三星|试图挽回中国市场,国际大厂不断调价,从高端机皇跌到传统旗舰价

- 魅族|魅族19配置曝光,天玑9000+三星E5直屏,网友: 来势汹汹!

- iqoo|iQOO Z5x兼备长续航与优质好屏,无压力畅玩游戏

- 任正非|任正非与孟晚舟的姓氏为什么不一样?

- 蓝思科技|苹果与34家中国供应商断绝合作,央视呼吁:尽快摆脱对苹果依赖

- 小米 11 Ultra 内测 NFC“读写勿扰”与“解锁后使用”功能

- iPhone|iphone14价格被曝!“胶囊”挖孔屏+三星4nm芯片,售价或5999起

- 三星|三星Galaxy S22参数曝光:仍有Exynos 2200处理器版本