cmos|Intel关键新突破:晶体管缩小50%、封装密度提升10倍

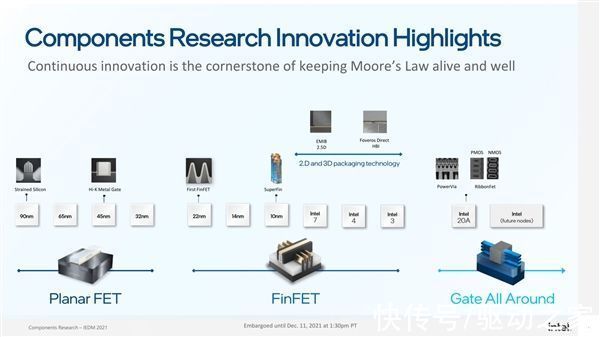

在日前的2021 IEEE IDM(国际电子器件会议)上,Intel公布、展示了在封装、晶体管、量子物理学方面的关键技术新突破,可推动摩尔定律继续发展,超越未来十年。

据介绍,Intel的组件研究团队致力于在三个关键领域进行创新:

文章插图

一是通过研究核心缩放技术,在未来产品中集成更多晶体管。

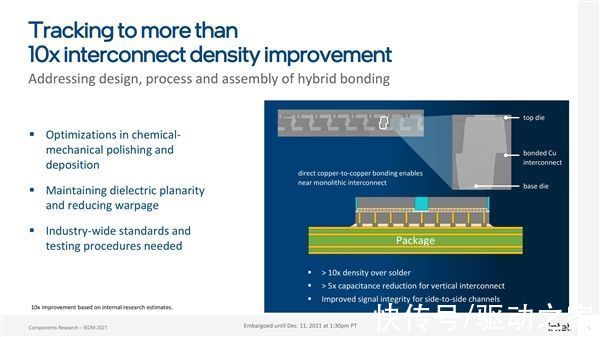

Intel计划通过混合键合(hybrid bonding),解决设计、制程工艺、组装难题,将封装互连密度提升10倍以上。

文章插图

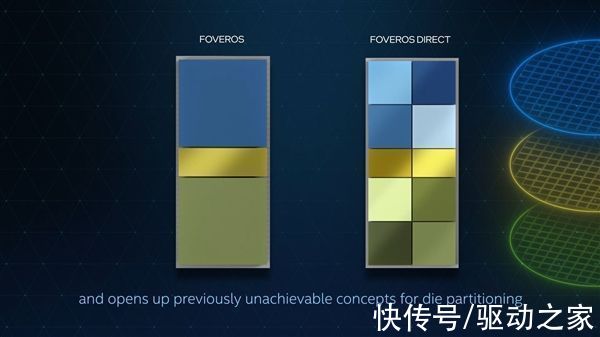

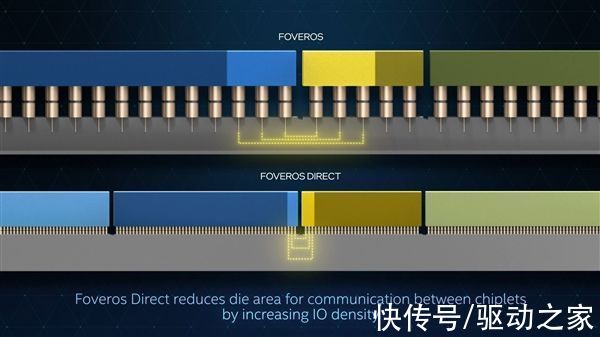

今年7月的时候,Intel就公布了新的Foveros Direct封装技术,可实现10微米以下的凸点间距,使3D堆叠的互连密度提高一个数量级。

文章插图

文章插图

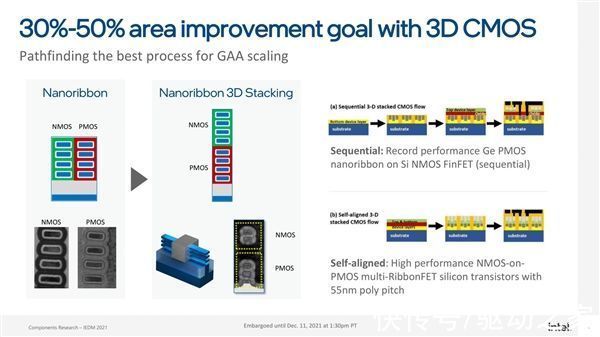

未来通过GAA RibbonFET晶体管、堆叠多个CMOS晶体管,Intel计划实现多达30-50%的逻辑电路缩放,在单位面积内容纳更多晶体管。

文章插图

后纳米时代,也就是埃米时代,Intel将克服传统硅通道的限制,用只有几个原子厚度的新型材料制造晶体管,可在每个芯片上增加数百万各晶体管。

文章插图

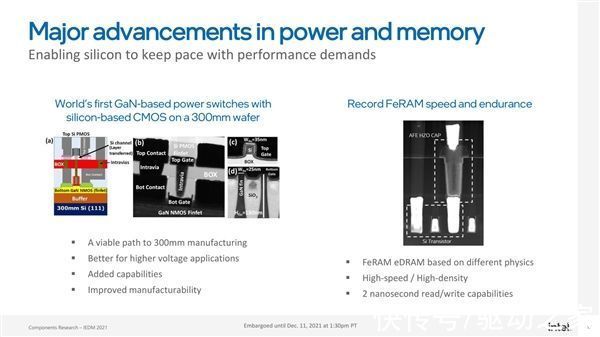

二是新的硅技术。

比如在300毫米晶圆上首次集成基于氮化镓的功率器件、硅基CMOS,实现更高效的电源技术,从而以更低损耗、更高速度为CPU供电,同时减少主板组件和占用空间。

比如利用新型铁电体材料,作为下一代嵌入式DRAM技术,可提供更大内存容量、更低时延读写。

文章插图

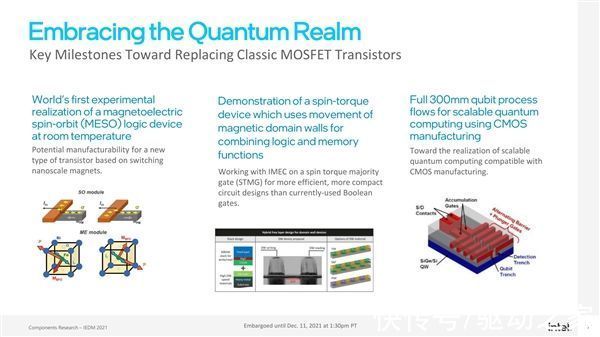

三是基于硅晶体管的量子计算、室温下进行大规模高效计算的全新器件,未来有望取代传统MOSFET晶体管。

比如全球首例常温磁电自旋轨道(MESO)逻辑器件,未来有可能基于纳米尺度的磁体器件制造出新型晶体管。

比如Intel和比利时微电子研究中心(IMEC)在自旋电子材料研究方面的进展,使器件集成研究接近实现自旋电子器件的全面实用化。

【 cmos|Intel关键新突破:晶体管缩小50%、封装密度提升10倍】比如完整的300毫米量子比特制程工艺流程,不仅可以持续缩小晶体管,还兼容CMOS制造流水线。

文章插图

文章插图

- 酷睿处理器|关键数据出炉,京东比阿里差远了

- Linux|电脑城卖的CPU是intel而不是AMD,和实体店不喜欢卖小米手机是一个道理

- 央媒表态后,联想关键数据出炉,柳传志这回要扳回一局?

- Intel找台积电打造专属3nm的工厂:并非短期合作?

- 工厂|为Intel单独建3nm工厂?台积电回应合作问题:不过度依赖单一客户

- intel公司|苹果芯片总监刚被Intel挖走,技术大咖又跳槽微软

- 英特尔|Intel未发布下代至强被开盖:完整64个核心、只开启56个

- Intel|Intel 13代酷睿新爆料!缓存将提升至68MB:游戏性能进一步增强

- Intel|下代至强处理器冲64核、350W Intel联合GRC开发CPU液冷散热技术

- meta|关键数据出炉,京东比阿里差远了