书籍:《炬丰科技-半导体工艺》

文章:湿法刻蚀三维集成电路硅片减薄技术

编号:JFKJ-21-666

作者:炬丰科技

索引术语-三维集成电路,硅通孔,TSV,湿法蚀刻,硅片,减薄技术。

摘要

三维集成电路技术已经发展成为半导体行业的新兴技术。硅片减薄是三维集成电路和硅通孔形成的关键技术之一。本文报道了三维集成电路硅片湿法刻蚀减薄技术。

介绍

通过应用摩尔定律,半导体已经小型化。然而,小型化的发展仍然是复杂性急剧增加和设备成本巨大的问题。另一方面,除了用于小型化的技术之外的技术已经被应用到高性能半导体的开发中。开发高性能半导体最有前途的技术是使用硅片(或芯片)减薄和硅通孔(TSV)的三维集成电路。这项技术为高性能半导体提供了以下优势:增加特定物理卷的内存容量;和更快的传输速度和更低的功耗,这是由于变薄和TSV效应提高了逻辑和存储器之间的响应能力。

实验和讨论

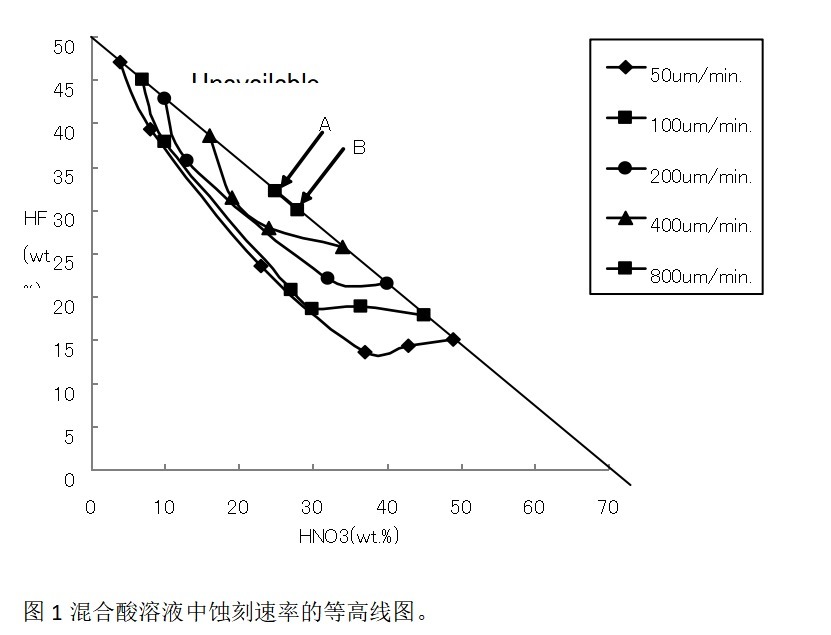

图1显示了蚀刻速率验证实验的结果。

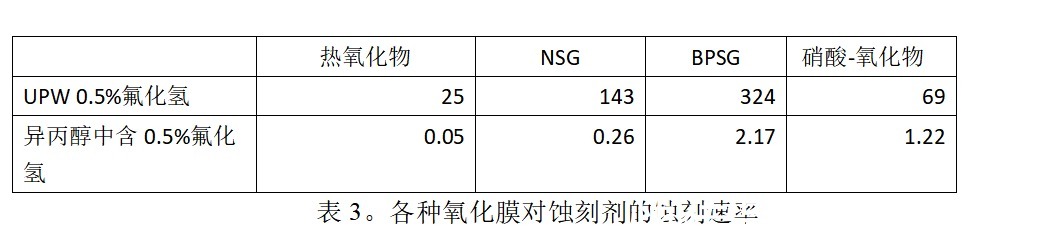

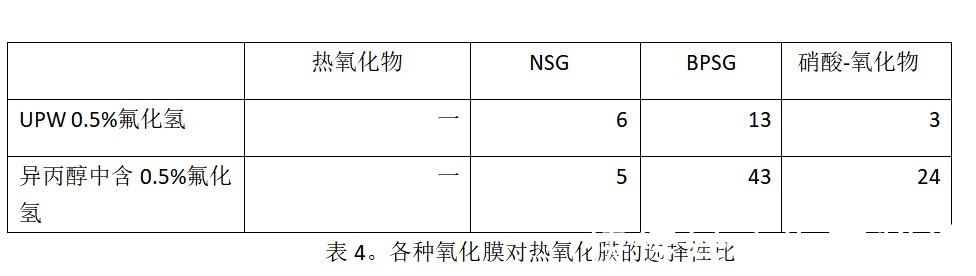

表3和表4显示了各种氧化膜的蚀刻速率以及根据蚀刻速率计算的它们对热氧化膜的选择性比率。与异丙醇溶液中的[1:24]相比,热氧化膜对水溶液中[1:3]的硝酸-氧化物的选择性表现出非常大的差异。这一结果表明热氧化膜不能被蚀刻,而存在可能蚀刻硝酸-氧化物的活性物质。用于本实验的异丙醇溶液中的氟化氢浓度明显小于水溶液中的浓度(1:0.03);然而,HF浓度实际上是相同的。这一结果表明,可能在异丙醇溶液中蚀刻硝酸-氧化物的反应物种被认为是中性的氟化氢。此外,硝酸-氧化物被认为不是完美的二氧化硅状态。

【 刻蚀|《炬丰科技-半导体工艺》湿法刻蚀三维集成电路硅片减薄技术】

文章插图

文章插图

文章插图

用旋转湿法刻蚀技术刻蚀硅片总蚀刻时间为1分钟,获得300 mm 10 mm的蚀刻量,总蚀刻时间为1.5分钟,获得450 mm 15 mm。这导致蚀刻量的均匀性为3%。此外,在晶片中心周围80毫米至100毫米的直径范围内,蚀刻量达到1%的均匀性。

总结

我们验证了通过使用全湿法蚀刻技术实现硅晶片的减薄而不会由于使用机械减薄技术(例如BG)而导致研磨损伤是可能的,并且展示了用于三维集成电路的高速率、精确硅晶片减薄蚀刻的潜力。结果,我们表明通过由HF和HNO3制备的混合酸化学溶液,在每片2分钟内减薄硅片是可能的。

- text|《2021大数据产业年度创新技术突破》榜重磅发布丨金猿奖

- 《吉星高照》的谢怜杀青啦,半年的拍摄

- 小米12|自研动态性能调度!小姐姐实测小米12 Pro《王者荣耀》:功耗下降20%

- 《消逝的光芒》开发商保证:游戏将获得 5 年的后续内容更新

- 《长津湖之水门桥》释出终极海报及剧照:准备战斗

- 今日|《战神4》pc版正式解锁dlss和fsr性能表现

- 《三生有幸遇上你》大结局:侯爵遇险,十一舍命相救

- 上海尊宝音响多款产品获《影音极品》器材大赏奖项

- 拯救者|首款无挖孔骁龙8旗舰!拯救者Y90实测30分钟《原神》平均帧率59.2

- 创新大赛|RTE创新大赛三强揭晓 !《实时互动场景创新生态报告》重磅发布